CZECH TECHNICAL UNIVERSITY IN PRAGUE Faculty of Information Technology

# Proceedings of the 7<sup>th</sup> Prague Embedded Systems Workshop

June 27-29, 2019 Roztoky u Prahy, Czech Republic

© Czech Technical University in Prague, 2019

ISBN 978-80-01-06607-2

Editors:

doc. Ing. Hana Kubátová, CSc. doc. Ing. Petr Fišer, Ph.D. Ing. Jaroslav Borecký, Ph.D.

# Message from the Program Chairs

The Prague Embedded Systems Workshop is a research meeting intended for the presentation of Ph.D. students' results and partial progress in their research in the field of all aspects of embedded systems design, including their testing, reliability, secure, safe, and low-power applications and communications. The workshop is organized annually by members of the Department of Digital Design of the Faculty of Information Technology of the Czech Technical University in Prague, for the seventh time this year. The main aim of PESW is to boost mutual discussions and establishing possible future cooperation between young researches not only inside EU. Therefore, the PESW workshop will be based on oral presentations and discussions.

There are three types of students' submissions and presentations at PESW 2019:

- Full papers describing the student's original research. These papers will undergo a standard reviewing process, and if accepted, they will be included in the Proceedings with ISBN.

- Abstracts of authors' earlier published and successfully presented papers (at conferences, journals, etc.). These contributions will not be reviewed; emphasis will be put on the presentation and discussion. These abstracts will be included in the Proceedings with ISBN.

- Student posters abstracts of defended Bc. and MSc. theses with subsequent poster presentation. These abstracts will not be included in the Proceedings.

16 papers were accepted for PESW 2019 presentation, from which there were 1 full paper and 15 abstracts. Contributions from Czech, Polish and Italian university research teams were accepted this year.

The technical program is also highlighted by three keynote speakers in the areas of security, testing, and network monitoring:

- Randomness in emerging technologies: Functional robustness vs. security. Speaker: Elena-Ioana Vatajelu, TIMA - CNRS / Université Grenoble Alpes, France

- Automotive testing challenges. Speaker: Paolo Bernardi, Politecnico di Torino, Italy

- Hardware Acceleration Techniques for Network Monitoring and Security. Speaker: Jan Kořenek, BUT, Brno, Czech Rep.; CESNET.

Seven technical sessions were formed, with the following topics:

- Fault Tolerance & Reliability

- Testing & Test Generation

- Security

- Cryptosystems & Cryptanalysis

- Network Monitoring

- Traffic Processing and Analysis

- Other

Last but not least we would like to thank to our sponsors (CTU in Prague, ASICentrum, STMicroelectronics, CESNET, CZ.NIC, ISECO.cz). Special thanks go to IEEE: IEEE Student Branch at Czech Technical University in Prague and IEEE Young Professionals, organizing student contest, and Czechoslovakia Section of IEEE.

We wish you to spend fruitful and communicative time in Roztoky.

# **Committees**

#### Workshop Chairs

Hana Kubátová, CTU in Prague (CZ) Petr Fišer, CTU in Prague (CZ)

#### Programme Committee (preliminary)

P. Bernardi, Politecnico di Torino (IT) A. Bosio, École Centrale de Lyon (FR) J. Buček, CTU in Prague (CZ) T. Čejka, CTU in Prague, Prague (CZ) G. Natale, TIMA, Grenoble (FR) P. Fišer, CTU in Prague, Prague (CZ) J.L. Gaudiot, University of California, Irvine (USA) I. Levin, Tel-Aviv University (IL) K. Jelemenská, STU Bratislava (SK) L. Kekely, BUT, Brno (CZ) P. Kitsos, TEI West. Greece (GR) Z. Kotásek, BUT, Brno (CZ) H. Kubátová, CTU in Prague, Prague (CZ) F. Leporati, Univ. di Pavia (GR) R. Lórencz, CTU in Prague (CZ) A. McEwan, University of Leicester (UK) N. Mentens, KU Leuven (BE) P. Mróz, University of Zielona Gora (PL) M. Novotný, CTU in Prague, Prague (CZ) A. Orailoglu, UC San Diego (USA) M. Ottavi, University of Rome (IT) E. Sanchez, Politecnico di Torino (IT) J. Schmidt, CTU in Prague, Prague (CZ) M. Skrbek, CTU in Prague, Prague (CZ) R. Stojanovic, Univ. of Podgorica Montenegro (ME) J. Strnadel, BUT, Brno (CZ) R. Ubar, Tallinn Univ. of Technology (EE) P. Velan, ICS MUNI (CZ) H.T. Vierhaus, Brandenburg University of Technology (DE)

W. Zając, University of Zielona Gora (PL)

# Special Session on Network Security Chair

Tomáš Čejka, CTU in Prague (CZ)

# **Student Poster Session Co-Chairs**

Tomáš Kolárik, CTU in Prague (CZ) Jan Bělohoubek, CTU in Prague (CZ)

# **Organizing Committee**

H. Kubátová, CTU in Prague (CZ)P. Fišer, CTU in Prague (CZ)R. Kinc, AMCA (CZ)E. Uhrová, AMCA (CZ)

# Contents

| Keynote 1: Randomness in emerging technologies: Functional robustness vs. securityElena-Ioana Vatajelu, TIMA - CNRS / Université Grenoble Alpes                               | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Keynote 2: Automotive testing challenges                                                                                                                                      | 2  |

| Keynote 3: Hardware Acceleration Techniques for Network Monitoring and Security Jan Kořenek, BUT, Brno, Czech Rep.; CESNET                                                    | 3  |

| Smart Electronic Locks and Their Reliability                                                                                                                                  | 4  |

| Fault Recovery for Coarse-Grained TMR Soft-Core Processor Using Partial Reconfiguration         and State Synchronization                                                     | 6  |

| Linear cryptanalysis and recovery of key bits in Baby Rijndael Josef Kokeš and Róbert Lórencz                                                                                 | 8  |

| Multiprecision Microcontroller-optimized ANSI C Library for Exotic Cryptosystems Jan Říha, Jakub Klemsa, and Martin Novotný                                                   | 10 |

| Recognition of Semi-trailers on the basis of the image                                                                                                                        | 11 |

| Multidimensional Pareto Frontiers Intersection: Processor Optimization Case Study Jakub Podivínský, Ondrej Čekan, MartinKrčma, Radek Burget, Tomáš Hruška, and Zdeněk Kotásek | 20 |

| The Future of Network Flow Monitoring                                                                                                                                         | 22 |

| Future approaches to monitoring in high-speed backbone networks                                                                                                               | 27 |

| L7 capable flow exporter described in P4                                                                                                                                      | 29 |

| A New Generation of an IPFIX Collector                                                                                                                                        | 33 |

| <b>Trace-Share: Towards Provable Network Traffic Measurement and Analysis</b>                                                                                                 | 35 |

| Multi-level Anomaly Detection in IoT Networks                                                                                                                                 | 37 |

| Low-Cost CMOS Power Consumption Data Dependence Demonstrator Concept Jan Bělohoubek and Robert Vik                                                                            | 39 |

| Analysis of the Dummy Rounds Scheme Optimizations                                                                                                                             | 40 |

| Health Monitoring and Fault Detection Using Memristive Switching Behavior in DSC Array .<br>Vishal Gupta, Jimson Mathew, and Marco Ottavi | 43 |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>PBO-Based Fault Selection for Compact Test Generation</b>                                                                              | 47 |

| Author Index                                                                                                                              | 49 |

| Sponsors                                                                                                                                  | 50 |

| Partners                                                                                                                                  | 52 |

# **Keynotes**

#### Randomness in emerging technologies: Functional robustness vs. security

#### Speaker: Elena-Ioana Vatajelu, TIMA - CNRS / Université Grenoble Alpes

The rapid development of low power, high density, high performance SoCs has pushed the CMOS devices to their limits and opened the field to the development of emerging technologies. The STT-MRAM and RRAM have emerged as promising choices for embedded memories due to their reduced read/write latency and high CMOS integration capability. Their inner properties make them ideal for implementation of memory blocks (mach and main memory) and, in addition, they are suitable for the implementation of basic security primitives such Physically Unclonable Functions (PUFs) and True Random Number Generators (TRNGs). PUFs are emerging primitives used to implement low-cost device authentication and secure secret key generation. On the other hand, TRNGs generate random numbers from a physical process. This talk will present a survey of today's and tomorrow's technologies and explain how it is possible to exploit (i) the high variability affecting the electrical device characteristics to build a robust, unclonable and unpredictable PUF, and (ii) the stochastic characteristics to generate randomly distributed numbers. In addition, it will underline the conflict between functional robustness and security quality of ICs designed with such devices.

#### Elena-Ioana Vatajelu

Dr. Elena-Ioana Vatajelu is a researcher with CNRS in TIMA Laboratory, Grenoble, France. She has 10 years of research experience in design, test and reliability of Integrated Circuits. She received a PhD in Electronic Engineering with distinction from Universitat Politècnica de Catalunya (Spain) in 2011. She has been involved in several European Projects (FP5 and FP7) and Spanish and Italian National projects. Dr. Vatajelu has served on the Technical Program Committees and Organizing Committees of conferences and symposia in design automation and test domains, such as DATE, IEEE VTS, IEEE ETS, IEEE DCIS, IEEE DDECS. Her main research interests are on reliability and robustness assessment, design-for-reliability, test strategies and security primitives for CMOS and beyond CMOS RAMs in traditional and non-Von Neumann computing (neuromorphic and CIM) paradigms. She has published 50 journal and conference papers in the area of dependable memories.

## Automotive testing challenges

#### Speaker: Paolo Bernardi, Politecnico di Torino, Italy

Manufacturing Automotive System-on-Chip is becoming always more challenging. That's because of the current complexity of the functionality to design, and also due to the very stringent quality requirements this kind of devices must meet. It is estimated that the quality aspects are weighting up to the 50% of the entire productive flow costs, since they "pollute" the conception of the chip with bulky test oriented circuitry and demand for several expensive test equipment to be used to ensure a perfect product being sold. The talk will depict a general scenario about all efforts to put in the manufacturing flow of a today's automotive chip, including technology qualification, design for testability, wafer sort/final test/burn-in/system level test, in-field self-test, certification tools and field return failure analysis.

#### **Paolo Bernardi**

Paolo Bernardi (MS'02 and PhD'06 in Computer Science) is an Associate Professor of the Politecnico di Torino University, where he works in the Electronic CAD and Reliability research group. His current interests includes System-on-Chip test and reliability, especially in the direction of high quality automotive devices. Prof. Bernardi is the General Chair of the Test Technology Educational Program (TTEP) and the Program Chair of the Automotive Reliability and Test (ART) Workshop held in conjunction with the International Test Conference. He was recently acting as Topic Chair for the European Test Symposium (ETS), the Design and Diagnosis of Electronic Circuits Symposium (DDECS) and the International On-Line Test Symposium (IOLTS). In 2018, he has been the General Chair of the Design and Technology of Integrated Circuits (DTIS) conference.

## Hardware Acceleration Techniques for Network Monitoring and Security

#### Speaker: Jan Kořenek, BUT, Brno, Czech Rep.; CESNET

High-speed packet processing is important especially in network monitoring and in security systems, where any packet drop can decrease the precision of monitoring or avoid detection or mitigation of malicious traffic. Current CPUs are not able to provide enough performance for security analysis of network traffic, especially in high-speed networks. To achieve wire-speed 100 Gbps throughput every packet has to be processed in less than 5 ns. Therefore the talk will summarise time-critical operations in network security systems, which require hardware acceleration. Then It will be introduced how deep pipelines, perfect hashing, and pipelined automata can help to achieve 100 Gbps packet processing of network security systems. The talk will address also the flexibility of hardware acceleration and integration of hardware architectures into future SmartNIC devices.

#### Jan Kořenek

Jan Kořenek is an associate professor at Brno University of Technology. Jan has been working since 2002 on many European and national research projects, where FPGA technology was used for an acceleration of IPv6 protocol routing, network traffic monitoring, NetFlow statistic measurement and fast regular expression matching in a packet payload. These projects provide substantial experiences in the hardware acceleration of algorithms for network applications and devices. Since 2003, He worked for CESNET as a leader of Hardware group at Liberouter project. In May 2007, He co-founded INVEA-TECH company which is a university spin-off focused on high speed network monitoring and security systems. Jan is an author and co-author of many novel hardware architectures, which has been used in commercially successful devices. For example, he is an co-author of COMBO-CG 100 Gb card, which received Czech Head award in the category Industria. His research interests are in the areas of hardware acceleration, reconfigurable architectures, embedded systems and network security and monitoring. Since 2012, He has been the head of Security and Administration Tools (SAT) department at CESNET. The SAT department is focused on research and development of new tools for network infrastructure. CESNET is an association of universities of the Czech Republic and the Czech Academy of Sciences.

#### **Smart Electronic Locks and Their Reliability**

Ondřej Čekan, Jakub Podivínský, Jakub Lojda, Richard Pánek, Martin Krčma, Zdeněk Kotásek Brno University of Technology, Faculty of Information Technology, Centre of Excellence IT4Innovations Božetěchova 2, 612 66 Brno, Czech Republic

Keywords. Electronic Lock, Stepper Motor, FPGA, Fault Tolerance, Stimuli Generation.

#### Abstract

Our research focuses on an analysis of electronic smart locks and explores the influences of faults on its controller unit. Electronic smart locks often utilize stepper motor as an actuator. Stepper motors, however, need a controller, which is usually implemented in a processor. The aim of our research is to examine the consequences of a failing controller processor. In our previous research, we developed a platform for fault tolerance testing with the ability to monitor the impacts on the mechanical part. We also developed a framework for accelerated testing of fault tolerance properties. The processor can be implemented in an FPGA (Field Programmable Gate Array) in order to be able to emulate HW faults inside the processor.

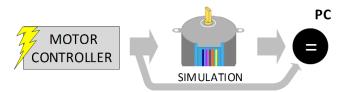

The concept of testing a smart lock is presented in Fig. 1, where all components are running on PC which allows us rapid prototyping and evaluation. Our experimental results utilizing the direct generation of invalid stimuli for the stepper motor. In our research, we found out that random errors probably could not be used for an unauthorized unlock, especially if the lock utilizes a mechanical gearbox. Deeper logic and knowledge of the correct sequence of steps used by the selected motor are needed to perform an attack to unlock the lock. On the other hand, random sequences could cause that lock not to be locked by falsifying the lock request sequence. The second interesting fact is that x% of faults in the valid sequence give the same rotation angle as 100-x% of faults.

Fig. 1: The concept of testing a smart lock – the first step.

#### Paper origin

The original paper has been accepted at 22<sup>nd</sup> Euromicro Conference on Digital System Design in Kallithea, Chalkidiki, Greece [1].

## Acknowledgment

This work was supported by The Ministry of Education, Youth and Sports from the National Programme of Sustainability (NPU II), the project IT4Innovations excellence in science - LQ1602, the BUT project FIT-S-17-3994 and the JU ECSEL Project SECREDAS (Product Security for Cross Domain Reliable Dependable Automated Systems), Grant agreement No. 783119.

## References

[1] Čekan, O.; Podivínský, J.; Lojda, J.; Pánek, R.; Krčma, M.; Kotásek, Z.: Testing Reliability of Smart Electronic Locks: Analysis and the First Steps Towards. In: 2019 Euromicro Conference on Digital System Design. Kallithea: IEEE Computer Society, 2019, accepted for publishing.

## Fault Recovery for Coarse-Grained TMR Soft-Core Processor Using Partial Reconfiguration and State Synchronization

Karel Szurman, Zdeněk Kotásek

Brno University of Technology, Faculty of Information Technology, IT4Innovations Centre of Excellence Bozetechova 1/2, 61266 Brno, Czech Republic

{iszurman, kotasek}@fit.vutbr.cz

Keywords. TMR, fault recovery, state synchronization, processor, FPGA reconfiguration

#### Abstract

SRAM FPGAs are being more commonly integrated into safety-critical systems nowadays. These digital circuits can provide suitable platform for a fault tolerant system implementation meeting the trade-offs between performance, reliability, cost and hardware resources. However, SRAM technology is vulnerable to radiation-induced faults and mainly to Single Event Upset (SEU) effect. The SEU can cause "bitflip" faults in SRAM memory cells which may affect internal FPGA routing (clock and reset signals), user memory (flip-flops, block RAM) and the functionality of implemented circuits. SEU mitigation must be implemented into the safety-critical design to achieve required system reliability in the harsh environment. SEU mitigation strategy may combine hardware redundancy and Partial Dynamic Reconfiguration (PDR) in order to implement error detection, self-repair ability and fault recovery mechanism into the system. With respect to the compromise between the system reliability and the resource overhead, various hardware redundancy schemes can be used. The most used form is Triple Modular Redundancy (TMR) which can be applied on different granularity levels in the system design. Coarse-grained TMR and PDR are often combined in one reconfigurable architecture. The time between SEU occurrence and the completion of fault recovery become a crucial parameter because the reliability of the TMR with one failed replica is worse than the reliability of an unprotected system. The fault recovery process can be generally divided into three phases: 1) fault detection, 2) fault removal by reconfiguration of a region containing replica identified as faulty, and 3) state synchronization bringing the reconfigured replica into the operating state consistent with other correctly operating replicas.

Combination of TMR and PDR is the approach also often addressed by fault mitigation methods designed for soft-core processors. The processor state is stored in internal memories and various architectural registers. After a faulty processor replica is reconfigured, its internal registers holding the processor state need to be synchronized with their up-to-dated copies from other processors replicas which were correctly operating. Various approaches had been proposed by researchers in the past. Four different synchronization methods which balance differently the trade-off between the synchronization speed and hardware overhead are evaluated in [2]. Synchronization of processors in known-blocking state by dumping and reading all processors data through shared Wishbone interconnection memory is presented in [3]. The largest amount of data which needs to be synchronized is the content of internal memories. With respect to a huge resource overhead, the use of a shared memory accessible from all three processor replicas is only practice solution. The critical part of the processor state synchronization is the maintenance of all internal registers. This requires implementation of a synchronization mechanism directly in the hardware to enable access to all registers and to minimize the synchronization time.

We propose a fault recovery mechanism for soft-core processor NEO430. In our PDR design, the NEO430 CPU core is protected by reconfigurable TMR architecture. In the TMR, the same input signals are shared between all CPU replicas and their output signals are brought into the majority voters. Each TMR voter is enhanced by additional error detection logic for identification of a failed CPU. The FPGA design floorplan is divided into two static and dynamic areas. Replicated CPU instances are placed into dedicated Partial Reconfiguration Modules (PRMs) in the dynamic area. Other design components are static; including reconfiguration controller GPDRC, synchronization controller and TMR voters. In the experiments, the reconfiguration of specific PRM corresponding to the faulty CPU replica is started based on the PRM error vector generated by TMR voters. A test application executed by triplicated CPUs periodically checks the digital input for activation of the synchronization enable request. This signal is generated by the GPDRC after the reconfiguration is finished. Afterwards, repaired CPU is restarted. During its startup, the test application reads the digital inputs and checks if request for synchronization is active. Since the request was activated by GPDRC, the CPU switches into the SLEEP mode. When the application executed by other operating CPUs is in a state suitable for synchronization, it will indicate readiness for the hardware synchronization through processor digital output to a synchronization controller. This is special circuit responsible for parallel addressing of all synchronized registers and their copying from the correctly working CPUs to the recovered one. Then, operating CPUs go into the SLEEP mode as well. In this state, CPUs are waiting for an external IRQ generated by the synchronization controller which will activate normal operating mode. In parallel, the synchronization controller performs synchronization of all internal registers while CPUs are idle in the SLEEP mode. After the hardware synchronization phase is finished, the external IRQ signal is triggered to bring CPUs again into the operating mode. Since that moment, all CPUs continue in synchronized program execution and with consistent data stored in the internal registers. By this FT design, we demonstrated possibility to implement a fault recovery mechanism for soft-core processor with the state synchronization logic embedded into the processor architecture and with the non-blocking CPU execution aware of fault recovery phases.

## **Paper origin**

This paper has been accepted and presented at the 22nd International Symposium on Design and Diagnostics of Electronic Circuits and Systems in Cluj-Napoca [1].

## Acknowledgment

This work was supported by The Ministry of Education, Youth and Sports from the National Programme of Sustainability (NPU II) project IT4Innovations excellence in science – LQ1602 and the BUT project FIT-S-17-3994.

## References

- Szurman, K.; Kotasek, Z.: Run-Time Reconfigurable Fault Tolerant Architecture for Soft-Core Processor neo430. 22nd International Symposium on Design and Diagnostics of Electronic Circuits and Systems. Cluj-Napoca: IEEE Computer Society, 2019, pp. 136-140. ISBN 978-1-72810-072-2.

- [2] Kretzschmar, U; Gomez-Cornejo, J.; Astarloa, A.; Bidarte, U.; Del Ser, J.: Synchronization Of Faulty Processors In Coarse-Grained TMR Protected Partially Reconfigurable FPGA Designs. Reliability Engineering & System Safety, 2016.

- [3] Morillo, A.; Astarloa, A.; Lazaro, J.; Bidarte, U.; Jimenez, J.: Knownblocking synchronization method for reliable processor using tmr & dpr in sram fpgas. VII Southern Conference on Programmable Logic (SPL), April 2011, pp. 57-62.

#### Linear cryptanalysis and recovery of key bits in Baby Rijndael

Josef Kokeš, Róbert Lórencz

Faculty of Information Technology, Czech Technical University in Prague Thákurova 9, Praha 6, 16000, Czech Republic

josef.kokes@fit.cvut.cz, robert.lorencz@fit.cvut.cz

**Keywords.** AES, Rijndael, Simplified AES, Baby Rijndael, Linear cryptanalysis, Key recovery.

#### Abstract

The Rijndael cipher, published in 1998 and standardized as AES in 2001 [1], is the most widely used symmetric block cipher in the world. It can be found in many practical applications, including disk and file encryption or messaging and communication. A very important are for AES is its appearance in various layers of network protocols such as WiFi or TLS/SSL where it serves to protect the integrity and confidentiality of transferred data.

To ensure the security of any cipher, cryptanalytic techniques are used to study the cipher and evaluate its resistance against various kinds of attacks, each based on specific assumptions. One of the basic techniques is the algebraic cryptanalysis, which tries to express the cipher as a set of equations, and its two special cases, differential cryptanalysis and linear cryptanalysis. Each modern cipher is designed with resistance to these techniques in mind, and AES is no exception [2], but even then these techniques may be successfully used to weaken the security of a cipher, as has been shown by the Biclique attack by Bodganov et al against full AES [3].

Unfortunately, the size of the full AES, which is an important part of its security as it prevents attacks using brute force, also makes it difficult to study in detail. We can, however, make use of the fact that unlike AES, which is highly constrained in its parameters [1], the description of Rijndael is quite open and allows modifications to many of its aspects. This has led to the introduction of several versions of simplified AES variants such as S-AES [4] or Baby Rijndael [5]. While these AES-variants cannot be practically used in real-world scenarios due to their reduced complexity, they strive to preserve as much of the original cipher's structure as possible while allowing a more detailed research due to their much more manageable sized.

In our past research of the effects of linear cryptanalysis on Baby Rijndael [6] we discovered several very interesting properties of the cipher. Particularly, we found out that when performing linear cryptanalysis using Matsui's Algorithm B [7], there are almost 8000 linear approximations with the theoretically best properties, which, however, achieve significantly different levels of success in recovering the cipher's key: For example, linear approximations which terminate in alternating active/inactive Sboxes in the second-to-last round of the cipher are on average much more successful than any other approximations. More, even within the same class of approximations, some approximations lead to better results than others: while the average rank of a recovered key for "bad" approximations is about 114 (out of 256), "good" approximations' correct key rank is about 49, with the actual rank varying between 40 and 57.

Furthermore, it appears that if we consider the bits of the recovered key individually, some bits tend to be more prone to errors than others; for example, bits 3 and 11 of the key can be successfully recovered

with a probability of as much as 70 %. Furthermore, some approximations tend to provide better results for some bits than the others, as has been shown by an exhaustive search of all the possibilities. With this fact in mind, we propose a set of algorithms which would leverage the varying success levels of key-bit recovery of different approximations to achieve an improved ratio of correct key recovery. We start with algorithms focused on the best recovery of a single bit of a key, leading up to a composite algorithm which would recover a set of bits with a higher-than-expected probability. The latest results have shown that we can correctly recover one bit of the key with a probability of more than 81 %. Four bits of the key can be correctly recovered with a probability of more than 49 %, which is a significant improvement over the theoretical 6,25 % of pure guessing.

We expect that a further improvement to these algorithms is possible, and that's where our current research is focused.

#### Acknowledgment

This research is supported by the the European Union<sup>1</sup>, The Ministry of Education, Youth and Sports of the Czech Republic, Czech Technical University in Prague and The Research Center for Informatics.

EUROPEAN UNION European Structural and Investment Funds Operational Programme Research, Development and Education

RESEARCH CENTER FOR INFORMATICS rci.cvut.cz

## References

- FIPS: Advanced Encryption Standard (AES), Federal Information Processing Standards, 2001, doi:10.6028/NIST.FIPS.197

- [2] Daemen, J., Rijmen, V.: The design of Rijndael: AES the Advanced Encryption Standard, Springer-Verlag, 2002, ISBN 3-540-42580-2.

- [3] Bogdanov, A., Khovratovich, D., Rechberger, C.: Biclique Cryptanalysis of the Full AES, Advances in Cryptology ASIACRYPT, 2011.

- [4] Musa, M., Schaefer E., Wedig S.: A simplified AES algorithm and its linear and differential cryptanalyses, Cryptologia 27, 2003.

- [5] Bergman C.: A Description of Baby Rijndael, Iowa State University, 2005.

- [6] Kokeš, J., Lórencz, R.: Linear Cryptanalysis of Baby Rijndael, IMACC, 2015.

- [7] Matsui, M.: Linear Cryptanalysis Method for DES Cipher, Lecture Notes in Computer Science, Vol. 765, 1994.

<sup>&</sup>lt;sup>1</sup>European Structural and Investment Funds, Operational Programme Research, Development and Education

# Multiprecision Microcontroller-optimized ANSI C Library for Exotic Cryptosystems

Jan Říha, Jakub Klemsa, Martin Novotný

Czech Technical University in Prague

rihajallfit.cvut.cz

Keywords. Cryptography, microcontroller, arithmetic.

## Abstract

Current cryptographic algorithms work with operands that are several times wider than the machine word, e.g., the still popular RSA algorithm shall use at least 2 048-bit keys. Such algorithms therefore require libraries that implement multiprecision arithmetic. Existing libraries are either not tailored for microcontrollers, or they implement an incomplete set of multiprecision operations, which limits the implementation of some unusual cryptographic algorithms on microcontrollers.

In this work, we present a novel ANSI C library that implements also some less common operations like, e.g., multiprecision integer division. The library was designed with respect to the use on microcontrollers and has been tested on ARM M4-based microcontroller Microchip CEC1302.

# **Paper origin**

This research has been presented at the 8th Mediterranean Conference on Embedded Computing (MECO 2019).

## Acknowledgment

This work was supported by the Grant Agency of the Czech Technical University in Prague, grants No. SGS17/213/OHK3/3T/18 and SGS19/109/OHK3/2T/13

#### **Recognition of Semi-trailers on the basis of the image**

**Tomasz Czech, Małgorzata Mazurkiewicz, Piotr Mróz, Anna Pławiak-Mowna** Faculty of Computer, Electrical and Control Engineering, University of Zielona Góra Address Prof. Z. Szafrana Street 2, 65 – 516 Zielona Góra, Poland

E-mail feralnex@gmail.com; m.mazurkiewicz@issi.uz.zgora.pl; p.mroz@imei.uz.zgora.pl; a.mowna@issi.uz.zgora.pl

**Abstract.** Due to the need of automatically determine the semi-trailer's identifier, a realtime identification system based on the camera image was developed. The article presents two methods of recognizing objects in an image. Both methods were tested and one of them was selected for implementation. The system was made and correctness tests were carried out. The system works properly and is used in tractor models with semi-trailers at the Faculty of Computer Science, Electrical Engineering and Automation at the University of Zielona Góra.

Keywords. Image recognition, object detection, vehicle control, ArUco markers.

#### **1** Introduction

For many years, the world has been working on the development of various types of vision systems. These systems are used, among others, for technological processes, monitoring of cities, air space, etc. One part of the process is to recognize objects in an image that can be performed on static image or from the moving camera. Face recognition, identification of license plates in cars, searching for cells on medical images are just a few of many examples of this rapidly growing branch of technology.

At the Faculty of Computer Science, Electrical Engineering and Automation of the University of Zielona Góra, a control system for the model of a truck with a semi-trailer made in 1:14 scale has been developed by students. The control is carried out using the manipulator shown in Figure 1. The manipulator allows you to control all the functions available in the saddle tractor model (speed, turn, selection of the gear, lighting, acoustic signal, etc.). Signals are sent to the truck (Figure 2). The control of the semi-trailer shown in Figure 3 is carried out from the manipulator via a truck tractor.

Currently, the department has four sets of vehicles (Figure 4) that can drive with any semi-trailer. All trucks and semi-trailers have the same addresses on the wireless bus, which means that the control is carried out with the currently turn on set. Ultimately, a modification of the manipulator program is planned, which will allow the operator to choose any truck. One of the problems that appeared during the implementation of this task is to indicate to the tractor the semi-trailer address to which he has driven and in which he controls the lighting, lifting the supports and read the battery voltage. In the described system, the identification should be carried out automatically, without the participation of the operator.

There was born an idea to identify automatically the semi-trailer that was connected to the truck, basing on the image from the camera placed on the back of the tractor cab (Figure 5).

Figure 1. The view of the manipulator

Figure 2. View of a tractor

Figure 3. View of the semi-trailer

Figure 4. Tractor units with semi-trailers located at the Faculty of Computer Science, Electrotechnics and Automation

## 2 Design assumptions

The tractors are equipped with two computers: STM32F4 Discovery - used to control the model, and Raspberry Pi 3 - used to acquire and transfer the image from one of the two cameras placed in the cabin of the vehicle. First camera - with wide angle - is placed at the front of the cabin and transmits an image seen from the front of the truck, the second one - ordinary - is placed in the back of the cabin and sends the image of the rear of the tractor and that what is behind it.

In order to build a system that identifies the kind of semi-trailer, it was assumed that:

- the system is operating on a Raspberry Pi computer built in the truck model,

- all operations used for the objects identification should be carried out without the participation of external data processing and analysis services,

- the data source with which the program will recognize the object is the image from the camera mounted in the rear of the truck cab (Figure 5),

- the system has to work correctly in a computer environment with limited hardware resources,

- it should be resistant to external conditions, eg. brightness of lighting,

- should identify the semi-trailer as soon as possible,

- beginning the recognition process takes place on a command sent via the UART interface from the truck control computer,

- the identification result has to be sent via the UART interface to the truck control computer.

Figure 5. View of the camera for recognizing the semi-trailer

## **3** Used method of Image analysis.

#### 3.1 Template matching method

The template matching method [3] is a model-based object recognition method. In this method it is necessary to create the so-called "repository of objects" (models base), which is used to compare the acquired image. The picture downloaded by the camera is compared with the pattern in the repository.

The object repository should contain all possible images that the recognition system will have to deal with. The reference images should be grouped according to the features of the object under study and then grouped into classes. During processing, firstly image classes are selected, and then specific pictures using matching method. This approach is aimed at reducing the number of comparisons [1, 2].

The main disadvantage is a huge number of patterns contained in the model database, what is necessary to use presented method. It leds to significant extention of the recognition time of the object.

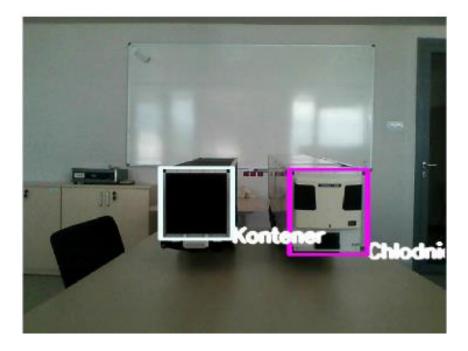

For the needs of the implemented project, a simple database of reference images containing photos of semi-trailers was created. Exemplary reference images of semi-trailers are presented in Fig. 6.

Figure 6. Exemplary reference images of semi-trailers

The program dedicated for Raspberry PI realizing the recognition of semi-trailers has been written in Python. The OpenCV (Open Source Computer Vision) library was used to process the image. It offers a lot of useful functions, which is using during image processing [5]. According to its authors, OpenCV has over 2,500 optimized algorithms.

During the tests, a program is run from the command line and the user can enter two parameters. The first one is responsible for accuracy and is given as a number between 0 and 1, for example the number 0.65 equals the accuracy of 65%. The accuracy is increasing with increase of value of this parameter. With an accuracy of more than 80-90%, for the program it is much harder to recognize the semi-trailer, while in the case of a set value below 50%, the program can recognize semi-trailers in other objects. The value from the range from 0.65 to 0.7 is assumed to be the optimal value, which allows to recognize the semi-trailer in an effective way. The second value entered by user determines the maximum timeout to recognize the semi-trailer. Exceeding this time interrupts the recognition and returns the "timeout" value.

The program can be run in two variants: the first one enables to display of the recognized model of the semi-trailer on the screen (Figure 7); the second variant allows to obtain the text identifier of the semi-trailer without displaying model on a screen (Figure 8). Research have shown that the time of recognition of a semi-trailer is from 2. This time depends of many factors, such as the brightness of the lighting, the angle between the tractor and the semi-trailer or the distance of the semi-trailer from the tractor.

Figure 7. Visual presentation of recognized semi-trailers

| naczepa_kontener<br>194 |  |

|-------------------------|--|

| naczepa_kontener        |  |

| 195<br>naczepa kontener |  |

| 196<br>naczepa kontener |  |

| 197                     |  |

| naczepa_kontener<br>198 |  |

| naczepa_kontener<br>199 |  |

| naczepa_kontener<br>200 |  |

| naczepa_kontener<br>201 |  |

| kontener                |  |

| exit 3                  |  |

Figure 8. Textual identifier of the semi-trailer

#### 3.2 ArUco markers

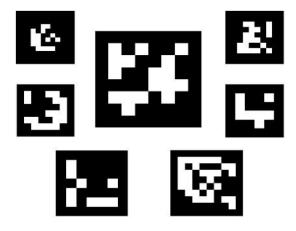

The ArUco marker (Figure 9) is a square tag composed of a wide black border and an internal binary matrix that specifies its identifier (id). The black border allows for quick image detection, and the binary codification enables its identification and lets to apply of error detection and correction techniques. The size of a marker determines the size of the inner matrix. For example, a 4x4 tag consists of 16 bits.

Figure 9. Examples of ArUco markers [7]

There are several types of markers, and each of them belongs to the dictionary. The design of the dictionary is important because its markers should be as different as it is possible to avoid misunderstandings.

The ArUco OpenSource library written in C ++ is used to detect ArUco markers on images [6]. Furthermore, if the camera is calibrated, you can estimate the camera's orientation relative to the markers. The result of identification of the semi-trailer by means of an exemplary mark is presented in Figure 10.

Application of the ArUco library in the program enabled real-time detection of marks placed on semi-trailers. In addition, drive of tractor to the semi-trailer can be made at different angles and from different distances. Studies have shown that the time of the semi-trailer recognizing ranges between 1 s to 5 s and it independent of the brightness and angle between the tractor and semi-trailer.

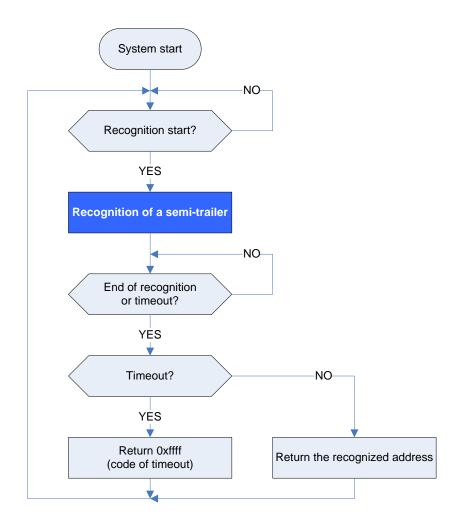

#### 4 System construction and testing

Based on the research described in p. 3, it was decided that the system being developed will use a program that uses ArUco marks. The system operation algorithm is shown in Fig. 11. It was implemented in Python using the OpenCV library and uploaded to the Raspberry Pi computer. In the next step implemented in the STM32F4 Discovery processor the truck control program was modified. After starting the Raspberry Pi processor, a system that waits for the order to start the recognition from the truck control processor sent via the UART interface is started. This order is sending when the semi-trailer is placed in the tractor's saddle. During the recognition of the semi-trailer, a counter controlling conversion time is also started. The process ends when the semi-trailer is recognized or after exceeding the prescribed time. Depending on the reason of ending the recognition by the UART interface, there is sent the code of the recognized semi-trailer or the 0xffff code, which informs that semi-trailer has not been recognized. To the STM32F4 Discovery processor was also added support for this command. When the ID of the detected semi-trailer is obtained, the address of the semi-trailer in the tractor is corrected and it is possible to control the created set. From now on, the system waits again for an order to start another conversion.

Figure 10. Identification of the semi-trailer with the use of a marker

## 5 Conclusion

Presented in the article methods of recognizing objects enabled the recognition of trucks semitrailers. In the case of the pattern matching method, due to the limited capacity of Rasphberry Pi memory, it may be problematic to create a sufficiently large database of patterns. Also the time of recognition of the object may be significantly extended due to the large number of patterns. Tests have shown that this method works the best when the tractor approaches the semi-trailer in line as near as possible to the straight line. Too much deviation can lead to anomalies in the objects recognition, eg. recognition of a semi-trailer in an object that is not. Furthermore, the brightness of the semi-trailer lighting has a very big impact on the recognition time.

The use of ArUco tags allowed to reduce the number of patterns, which significantly shortened the time of identification. In addition, it has been reduced influence of the lighting brightness. The developed system has been implemented and is used in truck models owned by the Faculty of Computer Science, Electrotechnics and Automation at the University of Zielona Góra.

Figure 11. System operation algorithm

#### References

- Szymczyk T., Metoda dopasowania wzorców w rozpoznawaniu obrazów ograniczenia, problemy i modyfikacje metody, Automatyka tom 12, zeszyt 2, UWND 2008, str. 449-462.

- [2] Choraś R. S.: Komputerowa Wizja Metody interpretacji i identyfikacji obiektów, EXIT Warszawa, 2005

- [3] T. Mahalakshmi, R. Muthaiah, P. Swaminathan, Review article: an overview of template matching technique in image processing, Res J Appl Sci, Eng Technol, 2012

- [4] Mai L. C.: Introduction to computer vision and image processing, Department of Pattern Recognition and Knowledge Engineering Institute of Information Technology, Hanoi, Vietnam eeexplore.ieee.org/iel5/10500/33260/01572091.pdf?arnumber=1572091.

- [5] OpenCV: http://sourceforge.net/projects/opencv/

- [6] ArUco: a minimal library for Augmented Reality applications based on OpenCV; https://www.uco.es/investiga/grupos/ava/node/26

- [7] Detection of ArUco Markers:

- [8] https://docs.opencv.org/3.1.0/d5/dae/tutorial\_aruco\_detection.html

## Multidimensional Pareto Frontiers Intersection: Processor Optimization Case Study

## Jakub Podivinsky, Ondrej Cekan, Martin Krcma, Radek Burget, Tomas Hruska, Zdenek Kotasek

Brno University of Technology, Faculty of Information Technology, Centre of Excellence IT4Innovations Božetěchova 2, 612 66 Brno, Czech Republic

Keywords. Pareto optimization, Pareto frontier, processor optimization, ASIP.

## Abstract

Almost all today's electronic devices are equipped with a processor. Different applications require and depend on different properties of the processor. For example, the fast-growing field of Internet of Things depends on a long operation time of the devices when powered with batteries. Using general purpose processors has proved ineffective which led to a growing usage of Application-Specific Instruction-Set processors (ASIPs) which can be optimized for specific applications using different modifications of their properties (such as the number of registers, cache sizes, instruction set modifications, etc.).

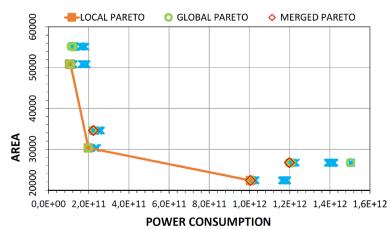

A suitable processor configuration can be hand-picked by a designer or by an automatic tool. Such a tool was developed in our previous research. It is able to find a set of Pareto-optimal processor configurations for a specific application which can be a significant help in a device design. The cost of the design process can be cut significantly when a processor is used in multiple designs. The goal of this paper is to introduce a tool able to find a suitable processor configuration for multiple applications by constructing a compromise Pareto-optimal frontier of processor configurations. The paper describes this problem on a theoretical level and it also introduces a practical implementation and experimental evaluation of constructing a compromise Pareto frontier of processor configurations for a set of applications. The experiments are based on a parametrizable RISC-V processor and example of compromise Pareto-optimal frontier is shown in Fig. 1.

Fig. 1: An example of all configurations (blue marks) with the original local and global Pareto frontiers together with merged Pareto frontier.

## Paper origin

The original paper has been accepted at 22<sup>nd</sup> Euromicro Conference on Digital System Design in Kallithea, Chalkidiki, Greece [1].

## Acknowledgment

This work was supported by The Ministry of Education, Youth and Sports from the National Programme of Sustainability (NPU II); project IT4Innovations excellence in science - LQ1602.

## References

J. Podivinsky, O. Cekan, M. Krcma, R. Burget, T. Hruska and Z. Kotasek. Multidimensional Pareto Frontiers Intersection Determination and Processor Optimization Case Study. In: 2019 Euromicro Conference on Digital System Design. Kallithea: IEEE Computer Society, 2019, accepted for publishing.

#### **Future Directions in Network Flow Monitoring**

Petr Velan

Masaryk University, Institute of Computer Science Botanická 68a, 60200, Brno

velan@ics.muni.cz

Keywords. Network, Flow Monitoring.

#### Abstract

Flow monitoring has been used for accounting and security for more than two decades. This paper describes how it was developed, what is its current status and what challenges can be expected in this field in the following years.

#### 1.1 The Past

The first mention of a flow export can be found in RFC 1272 [1] published in 1991 by IETF Internet Accounting (IA) Working Group (WG). The goal of the document was to provide background information on Internet accounting. The authors describe methods of metering and reporting network utilisation. The goal at the time was to provide a framework for traffic accounting. However, the common belief was that internet should be free and any form of traffic capture, even for the accounting purposes, is undesirable. This, together with the lack of vendor interest, resulted in the conclusion of the working group in 1993. Note that the negative attitude towards the monitoring returns more than 20 years later [2].

In 1995, Claffy, Braun, and Polyzos showed a methodology for internet traffic flow profiling based on packet aggregation [3], which started a revival of flow monitoring efforts. The Realtime Traffic Flow Measurement (RTFM) Working Group was active since 1996 and was conclude in 2000 by publishing several RFCs describing new traffic flow measurement framework with increased flexibility and even provided bi-directional flow support [4]. Since these documents fulfilled the objectives of the RTFM WG, the group was concluded in 2000. However, no flow export standard was developed as the vendors showed no interest in this area.

Meanwhile, Cisco realised that similar kind of flow information is already stored in a flow cache of their packet switching devices. The purpose of this cache is to speed up packet switching by making a forwarding decision only for the first packet of each flow. Unlike the RTFM flow measurement framework, the primary purpose of flow cache is not accounting nor monitoring. Therefore the configuration of measurement process using a flow cache in a switch is severely limited. Despite the limitations, once Cisco introduced its flow export technology called NetFlow, it achieved widespread adoption. The main reason for the wide adoption was the fact that it was readily available on most Cisco devices with little effort. The NetFlow was patented in 1996 and the first version that became available to the general public around 2002 was NetFlow v5 [5], albeit Cisco newer released any official specification. The NetFlow v5 format simply specified a single set of fields that should be exported from each flow record.

NetFlow v5 was soon obsoleted by NetFlow v9 which remedied some of the deficiencies of the previous version. The state of NetFlow v9 is described in [6]. It allowed defining an arbitrary set of

fields for export using templates. It also introduced support for new protocols, such as IPv6, Virtual Local Area Networks (VLAN), Multiprotocol Label Switching (MPLS), Border Gateway Protocol (BGP) or Multicast.

Other vendors created their own versions of flow exporting protocols, although they retained some level of compatibility with NetFlow. There are JFlow by Juniper, CFlow by Alcatel-Lucent, RFlow by Ericsson, and other protocols. When the potential of flow monitoring for security purposes became realised in 2005 [7], more effort was devoted to extending flow records with information not directly associated with switching. Cisco presented Flexible NetFlow technology [8] in 2006 which allows to dynamically define and export new types of information, such as parts of payloads or traffic identification.

In 2001, it was clear that exporting flow information from switching devices was going to be supported by vendors. However, no standard flow export protocol existed at the time and NetFlow v5 was not yet released to general public. For that reason the IETF started IP Flow Information Export (IP-FIX) WG [9]. The charter was updated over the years to match current requirements. Several vendors were engaged in the IPFIX WG's activities, most notably Cisco, which significantly contributed from the start. The WG defined a set of requirements for the IPFIX protocol [11] and evaluated existing candidate protocols [12] to decide the most suitable approach to defining the new protocol. The NetFlow v9 specification (RFC 3954) was designed with IPFIX requirements in mind [13] and was released in order to compete in this evaluation (RFC 3955). After the evaluation, the NetFlow v10 and even starts with protocol version 10 in its header. However, the IPFIX protocol supports many new features and is not completely backwards compatible with NetFlow.

The IPFIX WG did more than just design the IPFIX protocol. In the 29 RFCs published before its conclusion, the WG paid attention to, for example: bidirectional flow export, architecture for IP flow information export, reducing redundancy in flow and IP flow mediation framework. The IPFIX protocol specification is described by "Specification of the IP Flow Information Export (IPFIX) Protocol for the Exchange of Flow Information" [24] which became an Internet Standard. The working group was concluded in 2014, however, IPFIX related Internet-Drafts are still being created by involved parties. Further information about IPFIX development is provided by Brownlee in [25].

The importance of flow monitoring for security purposes was recognized by Cisco engineers in 2005 who proposed to use NetFlow for anomaly detection and traffic analysis [7]. Creation of dedicated flow monitoring probes allowed to easily extend the set of collected flow features and add application information to the flows. Pioneers in this area were Cisco, ntop, Masaryk Unviersity, and CESNET. Applications such as HTTP, DNS, and SMTP were being analysed. Cisco published a tool called *joy* [Cisco–Joy] in 2016 which allows to collect a rich set of information about network connections.

#### 1.2 The Now

A concern for privacy of users has been rising in recent years, which led to an extensive deployment of encryption of network traffic. It is more and more difficult to monitor network applications as most traffic is protected by TLS of other encryption protocols. HTTP/2 is supported only together with encryption by mainstream browsers. A recent push for addition of WireGuard VPN to Linux kernel has triggered its increasing adoption. However, despite the use of encryption, the need to monitor the traffic has not decreased. The challenge that we are facing is monitoring analysis of encrypted traffic.

Fortunately, machine learning algorithms are increasingly available as well; therefore statistical analysis of encrypted data can be performed with relative ease. There is a large body of research encrypted traffic classification and malware detection in encrypted traffic. The most recent results from Cisco show that information from TLS protocol together with per packet metrics can be used to achieve high accuracy in malware detection. However, flow records need to be extended with additional information to provide enough features for the machine learning algorithms.

#### 1.3 The Future

The level of encryption can be only expected to grow. There is an RFC draft called *Encrypted Server Name Indication for TLS 1.3* which proposes to encrypt even Server Name Indication in TLS protocol. Combined with increasing deployment of DNS over TLS and DNS over HTTPS protocols, most of the current visibility into network traffic will soon be lost. This will result in higher demand for statistical analysis of network traffic.

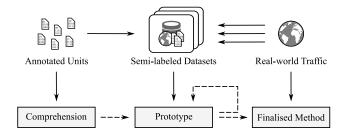

To obtain accurate results for encrypted traffic classification, an annotated dataset of high quality is needed. There are two approaches to obtain such datasets. The first is to observe and capture normal network traffic and manually or semi-automatically annotate it. The second approach is to generate the traffic manually and label the observed traffic based on the known traffic patterns. However, both approaches are time-consuming and error prone. Moreover, such datasets become obsolete in time and might not contain the necessary traffic mix that is seen in real networks. Therefore, the most of the research should be focused on generating and obtaining datasets that will enable us to perform encrypted traffic classification with high accuracy.

A promising way to obtain such datasets is to combine information from multiple sources, such as DNS resolvers, server logs, and application logs. This will allow us to assign labels to flow data with high accuracy and create datasets that are both real and of high quality. Once the data sets are available, machine learning can be used to find correlations and relations in the data, which can be used to analyse even non-labelled traffic. However, masquerading network traffic as a different category is just a next step that attackers are likely to be examining.

Apart from the encrypted traffic classification, there is also the question of quality of the generated data. For example, will the machine learning methods work well if flow generation parameters, such as timeouts, are changed? How are the flow exporters behaving under heavy load, are the exported flows incomplete? These and similar questions need to be answered, especially when machine learning is relied upon.

## Paper origin

The first part of this paper has been accepted as a dissertation of the author.

## Acknowledgment

This research was supported by ERDF "CyberSecurity, CyberCrime and Critical Information Infrastructures Center of Excellence" (No. CZ.02.1.01/0.0/0.0/16 019/0000822).

#### References

- C. Mills, D. Hirsh, and G.R. Ruth. *Internet Accounting: Background*. RFC 1272 (Informational). RFC. Fremont, CA, USA: RFC Editor, November 1991. URL: https://www.rfc-editor. org/rfc/rfc1272.txt (page 1).

- [2] S. Farrell and H. Tschofenig. *Pervasive Monitoring Is an Attack*. RFC 7258 (Best Current Practice). RFC. Fremont, CA, USA: RFC Editor, May 2014. URL: https://www.rfc-editor.org/rfc/rfc7258.txt (page 1).

- Kimberly C. Claffy, Hans-Werner Braun, and George C. Polyzos. "A Parameterizable Methodology for Internet Traffic Flow Profiling". In: *IEEE Journal on Selected Areas in Communications* 13.8 (October 1995), pp. 1481–1494. ISSN: 0733-8716. DOI: 10.1109/49.464717 (page 1).

- [4] N. Brownlee, C. Mills, and G. Ruth. *Traffic Flow Measurement: Architecture*. RFC 2722 (Informational). RFC. Fremont, CA, USA: RFC Editor, October 1999. URL: https://www.rfc-editor.org/rfc/rfc2722.txt (page 1).

- [5] Cisco Systems, Inc., San Jose, CA and USA. NetFlow Services Solutions Guide. January 2007. URL: http://www.cisco.com/en/US/docs/ios/solutions\_docs/netflow/ nfwhite.html (Accessed on April 27, 2017) (page 2).

- [6] B. Claise. Cisco Systems NetFlow Services Export Version 9. RFC 3954 (Informational). RFC. Fremont, CA, USA: RFC Editor, October 2004. URL: https://www.rfc-editor.org/ rfc/rfc3954.txt (page 2).

- [7] Cisco Systems, Inc., San Jose, CA and USA. Cisco IOS NetFlow and Security. February 2005. URL: http://www.cisco.com/en/US/prod/collateral/iosswrel/ps6537/ ps6586/ps6642/prod\_presentation0900aecd80311f49.pdf (Accessed on April 27, 2017) (page 2).

- [8] Cisco Systems, Inc., San Jose, CA and USA. Cisco IOS Flexible NetFlow. December 2008. URL: http://www.cisco.com/c/en/us/products/collateral/ios-nxos-software/flexible-netflow/product\_data\_sheet0900aecd804b590b. html (Accessed on April 27, 2017) (page 2).

- [9] The Internet Engineering Steering Group. IP Flow Information Export (ipfix) Charter. URL: http: //datatracker.ietf.org/wg/ipfix/charter/ (Accessed on April 27, 2017) (page 2).

- [10] The Internet Engineering Steering Group. IP Flow Information Export Charter. September 2001. URL: https://www.ietf.org/mail-archive/web/ipfix/current/msg00213. html (Accessed on April 27, 2017) (page 2).

- [11] J. Quittek et al. Requirements for IP Flow Information Export (IPFIX). RFC 3917 (Informational). RFC. Fremont, CA, USA: RFC Editor, October 2004. URL: https://www.rfc-editor. org/rfc/rfc3917.txt (page 2).

- [12] S. Leinen. Evaluation of Candidate Protocols for IP Flow Information Export (IPFIX). RFC 3955 (Informational). RFC. Fremont, CA, USA: RFC Editor, October 2004. URL: https://www.rfc-editor.org/rfc/rfc3955.txt (page 2).

- Brian Trammell and Elisa Boschi. "An Introduction to IP Flow Information Export (IPFIX)". In: *IEEE Communications Magazine* 49.4 (April 2011), pp. 89–95. ISSN: 0163-6804. DOI: 10.1109/MCOM.2011.5741152 (page 2).

- [14] B. Trammell and E. Boschi. Bidirectional Flow Export Using IP Flow Information Export (IP-FIX). RFC 5103 (Proposed Standard). RFC. Fremont, CA, USA: RFC Editor, January 2008. URL: https://www.rfc-editor.org/rfc/rfc5103.txt (page 2).

- [15] G. Sadasivan et al. Architecture for IP Flow Information Export. RFC 5470 (Informational). RFC. Updated by RFC 6183. Fremont, CA, USA: RFC Editor, March 2009. URL: https://www. rfc-editor.org/rfc/rfc5470.txt (page 2).

- [16] E. Boschi, L. Mark, and B. Claise. Reducing Redundancy in IP Flow Information Export (IPFIX) and Packet Sampling (PSAMP) Reports. RFC 5473 (Informational). RFC. Fremont, CA, USA: RFC Editor, March 2009. URL: https://www.rfc-editor.org/rfc/rfc5473.txt (page 2).

- [17] T. Dietz et al. Definitions of Managed Objects for IP Flow Information Export. RFC 5815 (Proposed Standard). RFC. Obsoleted by RFC 6615. Fremont, CA, USA: RFC Editor, April 2010. URL: https://www.rfc-editor.org/rfc/rfc5815.txt (page 2).

- [18] T. Dietz et al. Definitions of Managed Objects for IP Flow Information Export. RFC 6615 (Proposed Standard). RFC. Fremont, CA, USA: RFC Editor, June 2012. URL: https://www.rfc-editor.org/rfc/rfc6615.txt (page 2).

- [19] P. Aitken et al. Exporting MIB Variables Using the IP Flow Information Export (IPFIX) Protocol. RFC 8038 (Proposed Standard). RFC. Fremont, CA, USA: RFC Editor, May 2017. URL: https: //www.rfc-editor.org/rfc/rfc8038.txt (page 2).

- [20] A. Kobayashi and B. Claise. IP Flow Information Export (IPFIX) Mediation: Problem Statement. RFC 5982 (Informational). RFC. Fremont, CA, USA: RFC Editor, August 2010. URL: https: //www.rfc-editor.org/rfc/rfc5982.txt (page 2).

- [21] A. Kobayashi et al. IP Flow Information Export (IPFIX) Mediation: Framework. RFC 6183 (Informational). RFC. Fremont, CA, USA: RFC Editor, April 2011. URL: https://www.rfc-editor.org/rfc/rfc6183.txt (page 2).

- [22] E. Boschi and B. Trammell. IP Flow Anonymization Support. RFC 6235 (Experimental). RFC. Fremont, CA, USA: RFC Editor, May 2011. URL: https://www.rfc-editor.org/rfc/ rfc6235.txt (page 2).

- [23] G. Muenz, B. Claise, and P. Aitken. Configuration Data Model for the IP Flow Information Export (IPFIX) and Packet Sampling (PSAMP) Protocols. RFC 6728 (Proposed Standard). RFC. Fremont, CA, USA: RFC Editor, October 2012. URL: https://www.rfc-editor.org/rfc/rfc6728.txt (page 3).

- [24] B. Claise, B. Trammell, and P. Aitken. Specification of the IP Flow Information Export (IPFIX) Protocol for the Exchange of Flow Information. RFC 7011 (Internet Standard). RFC. Fremont, CA, USA: RFC Editor, September 2013. URL: https://www.rfc-editor.org/rfc/ rfc7011.txt (page 3).

- [25] Nevil Brownlee. "Flow-Based Measurement: IPFIX Development and Deployment". In: *IEICE Transactions on Communications* E94.B.8 (September 2011), pp. 2190–2198. DOI: 10.1587/transcom.E94.B.2190 (page 3).

#### Future approaches to monitoring in high-speed backbone networks

Karel Hynek, Tomáš Beneš, Tomáš Čejka, Hana Kubatová FIT Czech Technical University in Prague CESNET a.l.e.

Thákurova 9, Prague 6 Zikova 4, Prague 6

hynekkar@fit.cvut.cz, benesto3@fit.cvut.cz, tomas.cejka@fit.cvut.cz, kubatova@fit.cvut.cz

Keywords. Network, Monitoring, Analysis, Encryption, Security, Hardware

#### Abstract

Network monitoring features has been always a challenge in high-speed networks. Some of them like detailed traffic analysis and packet inspection are not suited or simply not feasible even on modern hardware. The challenges are becoming even greater with an uprise of encrypted traffic. This leaves large opportunity for threat actors to take advantage of. Therefore, it is necessary to develop a new generation of monitoring tools that can deal with the current issues for security purposes. This research aims to improve traffic analysis techniques to handle encrypted traffic, and also to adapt hardware accelerated monitoring components for processing.

#### 2 Introduction

Personal privacy became one of the crucial features of modern applications in recent years. Due to surveillance, fraudulent attempts and data leaks scandals companies are forced by the public opinion to strengthen their services by use of encryption.

Gartner predicts (1) that by the end of 2019, 80 percent of internet traffic will be encrypted. There is simply no reason NOT to encrypt anymore. This prevents any surveillance possible and allows users to have their privacy secured. However, this enables threat actors to hide malicious activities on the network.

This introduces the new field of research, where a traditional threat inspection with bulk decryption, analysis and re-encryption is not always practical or feasible, for performance and resource reasons.

Detection of malicious and non-standard activities in encrypted communication is one of the new challenges. Most of the businesses do not have tools capable of analyzing these threats in encrypted connections at their disposal. This leaves these businesses vulnerable to many threats.

There are several proprietary solutions targeted on detecting anomalies in encrypted connections (1). These solutions aims to be deployed at large businesses and are not intended to be used in the open source form. This gives us a great opportunity to introduce new types of threat detection algorithms aimed at encrypted communication.

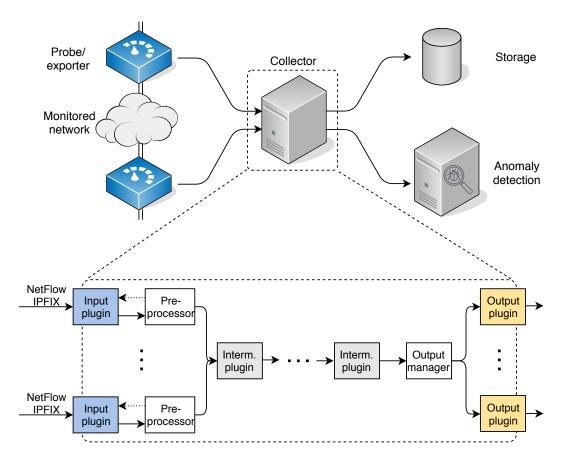

#### **3** Monitoring infrastructure for future

Traditional infrastructure for network monitoring is composed of monitoring probes, also known as observation points, that aggregate packet-level information and extract protocol headers. These information are sent in a form of IP flow records into a flow collector, where the data are processed and stored.

Flow data usually contain information about transport layer protocols, i.e., IP addresses, transport layer protocol, and transport protocol ports. Additional information can be extracted from the application layer in case of not encrypted traffic. Recently, there have been developed tools (2) for this purpose. However, the amount of encrypted traffic is increasing, where the application layer is not available.

Evolution in encrypted traffic analysis starts with Joy flow exporter (3), that is designed to extract data features, i.e., inter packet gaps, the sequence of lengths and arrival times of TLS records etc., from network traffic. The computed features can be used with machine learning tools for classification and anomaly detection. However, this approach is very dependent on training datasets that are generally not easily available.

Monitoring probes for high-speed network links need to be hardware accelerated. Development of such high-performance devices is a non-trivial task. The devices must be intensively optimized for specific purposes, such as header field extraction or computation of traffic-related statistics. On the other hand, there is a software-defined networking concept that describes the functionality with more abstraction using either configuration mechanisms or even application specific high-level languages. Benáček et al. presented a generation of high-speed (at least 100 G) devices from the P4 (4) language in (5). Also, Havranek et al. proposed enhanced flow exporter described in P4 capable of processing multi-layer encapsulation in (6).

The aim of our research is to improve the flow-based network monitoring concept for encrypted traffic. It will based upon the current state-of-the-art, which is represented by the latest Cisco systems activities related to botnet detection in encrypted traffic using machine learning. The theoretical part of the work lies in traffic analysis and derivation of models that can be used for the recognition and classification of network traffic. Theoretical findings, evaluated by experiments with real network traffic, will be applied to design and develop a new generation of hardware-accelerated monitoring probes that can provide required traffic features for classification and detection models. The main goal of the hardware scope of the work aims to explore promising technology of high-level synthesis using P4 language to describe a hardware-accelerated monitoring probe. However, the synthesis from P4 language into sufficient high-throughput hardware design (e.g., in VHDL) is not currently not available and must be elaborated.

#### 4 Conclusion

This paper presents a first insight into our planned research related to a new generation of flowbased network monitoring system consisting of hardware-accelerated monitoring probes and classification/detection software capable of analysis of encrypted traffic in high-speed backbone networks.

The planned solution will be a continuation of the current research activities at Faculty of Information Technology in collaboration with CESNET association, which is the operator of the Czech national research and education network.

#### Acknowledgment

This research has been supported by the CTU grant projects SGS17/017/OHK3/1T/18 "Dependable and attack-resistant architectures for programmable devices" and SGS17/212/OHK3/3T/18 "Research and development of tools for security analysis of computer network traffic"

#### References

- [1] Encrypted Traffic Analytics, Cisco Systems 2019. [Online]. Available: https://www.cisco.com/c/dam/en/us/solutions/collateral/enterprise-networks/enterprise-networksecurity/nb-09-encrytd-traf-anlytcs-wp-cte-en.pdf

- [2] Čejka, T.: Stream-wise Parallel Anomaly Detection in Computer Networks, Ph.D. thesis, Faculty of information technology, CTU in Prague, 2018.

- [3] Anderson, B., McGrew, D.: Joy. 2016. [Online]. Available: https://github.com/davidmcgrew/joy

- [4] P4 language, https://p4.org/

- [5] Benáček, P., Puš, V., Kubátová, H., Čejka, T.: P4-to-VHDL: Automatic Generation of High-Speed Input and Output Network Blocks. In: Microprocessors and Microsystems journal (MICPRO, Volume: 56), DOI: 10.1016/j.micpro.2017.10.012., Elsevier, 2018.

- [6] Havránek, J., Velan, P., Cejka, T., Benáček, P.: Enhanced Flow Monitoring with P4 Generated Flexible Packet Parser. In proceedings AIMS 2018, 2018.

#### L7 capable flow exporter described in P4

**Jiří Havránek Tomáš Čejka Pavel Benáček** FIT CTU in Prague CESNET, a.l.e. Thákurova 9, 160 00 Prague 6, Czech Republic

{havraji6,tomas.cejka}@fit.cvut.cz benacek@cesnet.cz

Keywords. P4, compiler, backend, code generation, flow exporter, application protocols

#### Abstract

Current flow exporters are the essential source of information for monitoring systems. They usually create aggregated information as flow data and, additionally, it is possible to extract headers from higher layer protocols (L7). Due to requirements on high throughput, the flow exporters use hardware acceleration to handle high packet rate at link speed (aiming at least 100 Gb/s). However, manually created design of such high-performance devices is very complex and complicated. Therefore, we propose to use a high-level P4 language for description of network traffic processing device that will be capable of handling L7 information. As our recent works show, it is possible to generate high-performance firmware design automatically based on P4 description. Since P4 is not primarily intended for processing L7 data, this paper proposes a feasible way to overcome limits of P4.

#### 2 Introduction

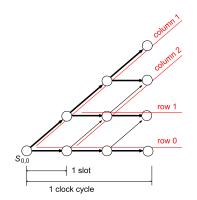

As computer networks grows rapidly, the infrastructure needs technology that is more flexible. In the recent history a software defined networking concept was introduced by Open Networking Foundation. It is based on flexible configuration of network active devices at run-time by a special element — controller — that has a global overview about network traffic.

The next evolution step brought more flexibility to network devices itself. P4 consortium has defined an universal architecture of network active devices (L2–L4 switches) that is composed of a parser, match action tables, and deparser. To describe functionality of all three components, a novel high-level application specific language called P4 was proposed. Based on P4 description, which is much simpler than low-level programming languages (such as C/C++) or hardware definition languages (such as VHDL). Naturally, the primary goal of P4 is to translate the description into real compiled or synthesized functional blocks usable in the device.

P4 consortium develops and maintains a compiler that is able to generate code for target platform using so called backend, i.e., part of the compiler. Section 3 describes several existing backends. However, we see the limits of P4 that are related to the capabilities of the language and standardized architecture. Our aim is to enhance possible use-cases of P4 to be able to process L7 protocols. As a proof-of-concept, we have created a P4 description of flow exporter, a system that aggregates packet-level information into flow data in IPFIX [1], and is able to extract even L7 information. The description is compilable using the developed backend for P4 compiler.

#### **3** Related Work

There are few existing compiler backends for various P4 applications at the moment. The example of such backends can be the compiler from P4 to HDL language which is used for the description of digital circuits. This can be beneficially used for fast development of network accelerators because HDL language is much more complicated compared to the P4 or C language. One of the emerging works from this area was described in [5]. There are also backends for different languages like transformation from P4 to C. However, none of currently known backends deals with automatic generation of flow exporter, but there are ones that can be used to generate flow exporter parts.

One of the existing backends is Flexible Packet Parser (FPP) backend [2] that was developed as our recent work. It deals with generation of packet parser described in P4 and generates C code with parsing function. This generated parser is capable of parsing unlimited number of protocol headers and tunnel encapsulation. The output of the parser are extracted headers in form of linked list. Headers to extract can be specified in special P4, architecture defined, structure.

Other backends with parser include generation of eBPF [3] and XDP [4] filters. Compiler generates C code of filters that can be compiled into filter program and loaded into kernel.

## 4 L7 processing

Our research is a continuation of the development L7 capable flow exporter that was written manually. Based on the analysis and our experiences, we have identified the following requirements to be able to process L7 headers:

- 1. Extract string with moving payload cursor

- 2. Match string in payload without moving payload cursor

- 3. Match extracted string

- 4. Convert extracted string to number

- 5. Copy strings between variables

All the listed function must be supported by the device in order to extract the needed information that should be put into IPFIX records. Luckily, P4 has a construct that represent an external block (*extern block*) with functionality "hidden" inside. The *extern blocks* are a standard way to express counters in P4 language (version 16). Therefore, the functions we listed are represent as *extern blocks* and are supported by our P4 backend.

## 5 Flow Exporter Generated from P4

During flow exporter analysis, key architecture components were identified. These components are necessary to describe packet headers processing, application protocol processing, flow creation and export process of generated exporter in P4 language. They include packet parser, flow record create/update/export functions and application protocol parsing plugins.

C code with flow exporter is generated by P4 compiler backend developed by this work. Code generation of exporter requires P4 program and exporter source code templates. C source code templates contain placeholders for variable rendering like {{ plugin/name }}. These placeholders are replaced by backend with generated code when compiling P4 program with described exporter components. Generated source codes of exporter can be later compiled into executable application.

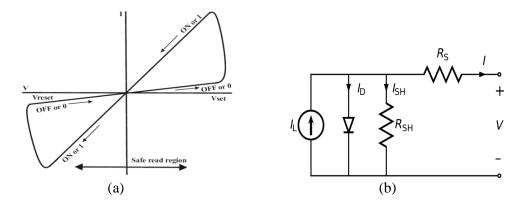

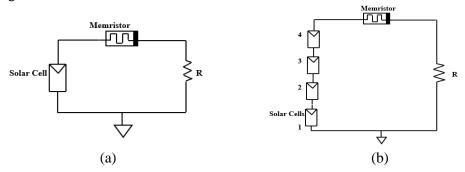

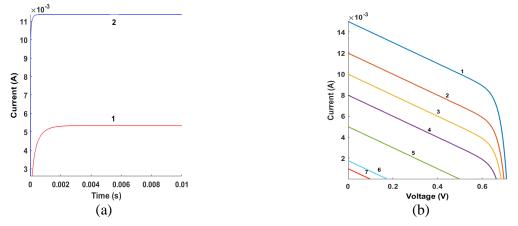

Architecture of P4 program consist of P4 parser and control blocks, used to describe functionality of each component of exporter. For every parser and control block in the program, there is an apropriate extern block available to use. These extern blocks help to represent exporter specific functionality like creation of flow key, creation of IPFIX templates, adding flow fields to IPFIX packet, parsing L7 protocols etc.